# UM10208 LPC2880/LPC2888 User manual Rev. 02 — 31 May 2007

User manual

#### **Document information**

| Info     | Content                                                                                  |

|----------|------------------------------------------------------------------------------------------|

| Keywords | LPC2880, LPC2888, LPC288x, ARM, ARM7, embedded, 32-bit, microcontroller, USB 2.0, USB HS |

| Abstract | LPC288x User manual                                                                      |

LPC288x User manual

#### **Revision history**

| Rev | Date     | Description                                                                                                                                  |

|-----|----------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 02  | 20070531 | Various editorial and content updates to the following chapters:                                                                             |

|     |          | <ul> <li>The format of this user manual has been redesigned to comply with the new identity<br/>guidelines of NXP Semiconductors.</li> </ul> |

|     |          | <ul> <li>Legal texts have been adapted to the new company name where appropriate.</li> </ul>                                                 |

|     |          | <ul> <li>Universal Asynchronous Receiver-Transmitter (UART):</li> </ul>                                                                      |

|     |          | The UART baud rate is derived from the UART baud rate clock (UART_CLK).                                                                      |

|     |          | <ul> <li>External Memory Controller (EMC):</li> </ul>                                                                                        |

|     |          | SDRAM Usage notes added (Section 8–12).                                                                                                      |

|     |          | <ul> <li>Clock Generation Unit (CGU) and power control:</li> </ul>                                                                           |

|     |          | CGU Usage notes added including a section on how to achieve low-power operation (Section 7–5).                                               |

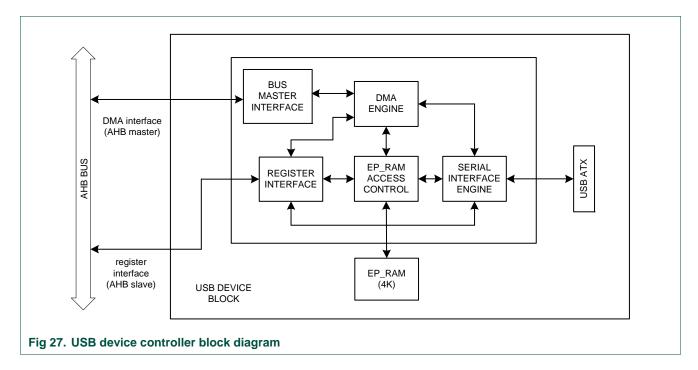

|     |          | USB Device controller:                                                                                                                       |

|     |          | <ul> <li>DMA mode transfer section was improved (<u>Section 17–6.4</u>).</li> </ul>                                                          |

|     |          | <ul> <li>Endpoint configuration table added (<u>Table 17–232</u>).</li> </ul>                                                                |

|     |          | <ul> <li>Section 17–8.6 on interrupt handling was further elaborated.</li> </ul>                                                             |

|     |          | • I/O pinning:                                                                                                                               |

|     |          | Section 25–2.5 "Pin structure" added.                                                                                                        |

|     |          | DC-to-DC converter:                                                                                                                          |

|     |          | Section 6–2 "General operation" was improved.                                                                                                |

|     |          | SD/MMC interface:                                                                                                                            |

|     |          | Status register contents were corrected ( <u>Table 23–345</u> ). Descriptions on bits 17 and 19 were swapped.                                |

|     |          | <ul> <li>General Purpose DMA controller (GPDMA):</li> </ul>                                                                                  |

|     |          | Register locations for registers DMA3EXTEN and DMA5EXTEN were corrected (Table 15–196).                                                      |

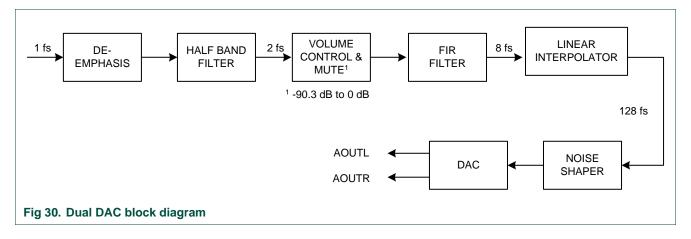

|     |          | <ul> <li>Dual-channel 16-bit Digital-to-Analog Converter (DDAC):</li> </ul>                                                                  |

|     |          | <ul> <li>Description of Dual DAC was improved.</li> </ul>                                                                                    |

|     |          | <ul> <li>Section 22–6.2 "Power-up procedure" was corrected.</li> </ul>                                                                       |

|     |          | <ul> <li>Dual-channel 16-bit Analog-to-Digital converter (DADC):</li> </ul>                                                                  |

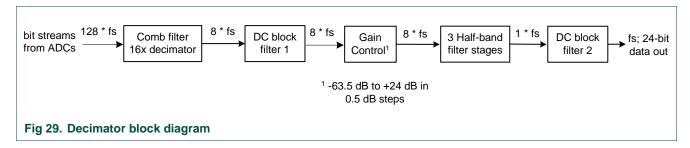

|     |          | Bits 0-7 of Decimator Control register were corrected (Table 21–306).                                                                        |

|     |          | • I <sup>2</sup> S output module (DAO):                                                                                                      |

|     |          | DAO pin description was corrected (Table 20-292).                                                                                            |

|     |          | Boot process:                                                                                                                                |

|     |          | Part Identification register ( <u>Table 3–4</u> ) was moved to this chapter from chapter "System control".                                   |

|     |          | Chapter "System control" removed.                                                                                                            |

|     |          | <ul> <li>Chapter "General Purpose I/O (GPIO)" added.</li> </ul>                                                                              |

| 01  | 20060905 | LPC288x User manual                                                                                                                          |

## **Contact information**

For additional information, please visit: <a href="http://www.nxp.com">http://www.nxp.com</a>

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

# **UM10208**

# **Chapter 1: Introductory information**

Rev. 02 — 31 May 2007

**User manual**

#### 1. Introduction

The LPC288x is an ARM7-based microcontroller for portable applications requiring low power and high performance. It includes a USB 2.0 High Speed device interface, an external memory interface that can interface to SDRAM and Flash, an MMC/SD memory card interface, A/D and D/A converters, and serial interfaces including UART, I<sup>2</sup>C, and I<sup>2</sup>S. Architectural enhancements like multi-channel DMA, processor cache, simultaneous operations on multiple internal buses, and flexible clock generation help ensure that the LPC288x can handle more demanding applications than many competing devices. The chip can be powered from a single battery, from the USB, or from regulated 1.8 and 3.3V.

#### 2. Features

- ARM7TDMI processor with 8 kB cache operating at up to 60 MHz

- 1 MB on-chip Flash Program Memory with 128-bit access for high performance

- 64 kB SRAM

- 32 kB ROM

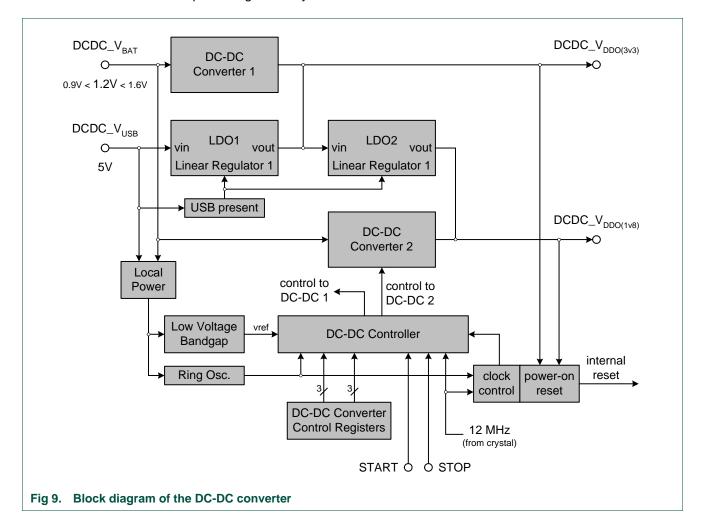

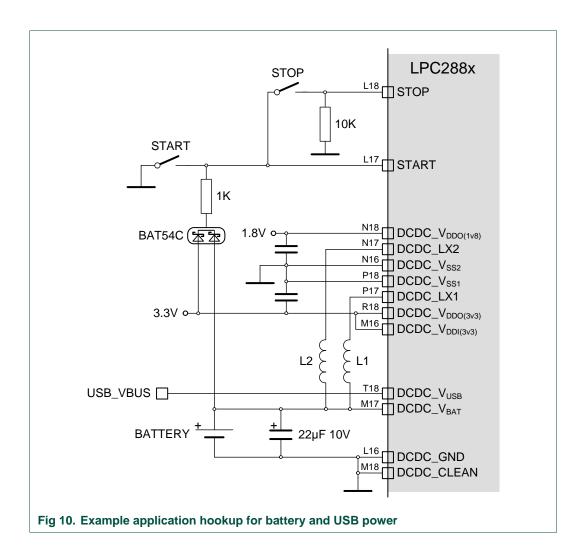

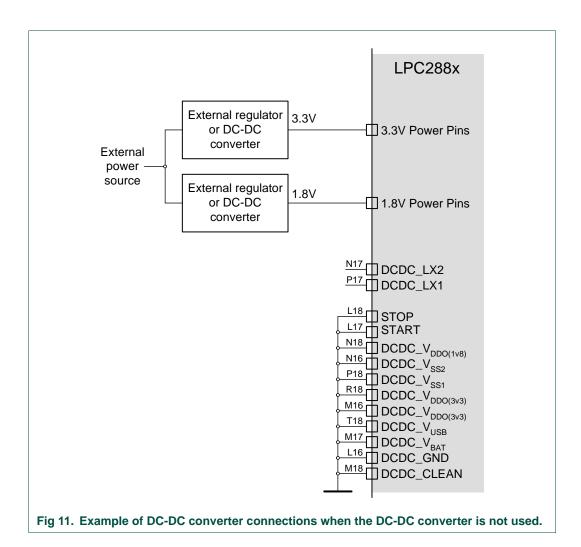

- On-chip DC-DC converter can generate all required voltages from a single battery or from USB power

- Multiple internal buses allow simultaneous GP DMA, USB DMA, and program execution from on-chip Flash without contention.

- External memory controller supports Flash, SRAM, ROM, and SDRAM.

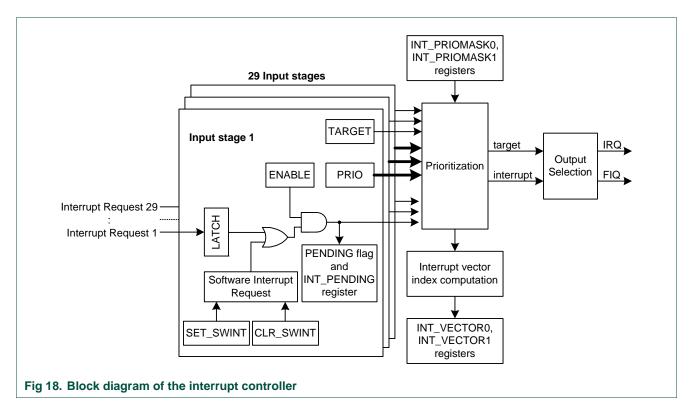

- Advanced Vectored Interrupt Controller, supporting up to 30 vectored interrupts

- Innovative Event Router allows interrupt, power-up, and clock-start capabilities from up to 105 sources

- Multi-channel GP DMA controller that can be used with most on-chip peripherals as well as for memory-to-memory transfers.

- Serial Interfaces:

- Hi-Speed or Full-speed USB 2.0 Device (480 or 12 Mbits/s) with on-chip PHYsical layer

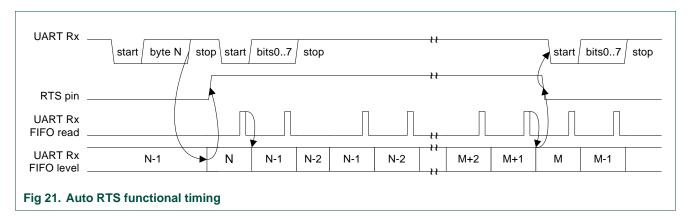

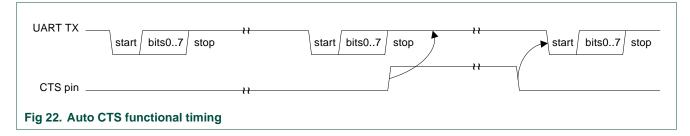

- UART with fractional baud rate generation, flow control, IrDA support, and FIFOs

- I<sup>2</sup>C Interface

- I2S (Inter-IC Sound) interface for independent stereo digital audio input and output

- Secure Digital (SD) / MultiMediaCard (MMC) memory card interface

- 10 bit A/D Converter with 5-channel input multiplexing

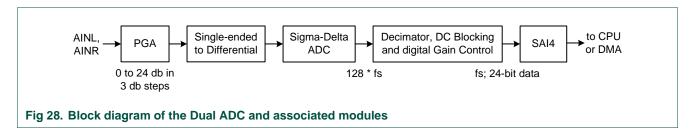

- 16 bit stereo A/D and D/A converters with gain control and optional DMA

- Advanced clock generation and power control reduce power consumption

- Two 32-bit Timers with selectable prescalers

- 8-bit LCD interface bus

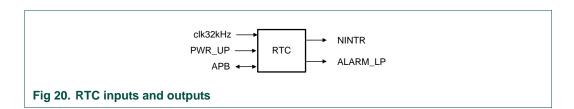

- Real Time Clock can be clocked by 32 kHz oscillator or another source

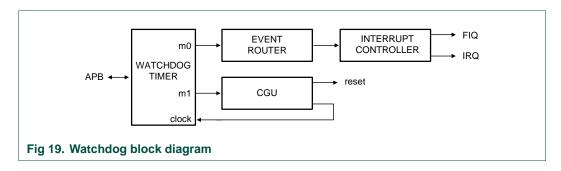

- Watchdog Timer with interrupt and/or reset capabilities

#### **Chapter 1: LPC2800 Introductory information**

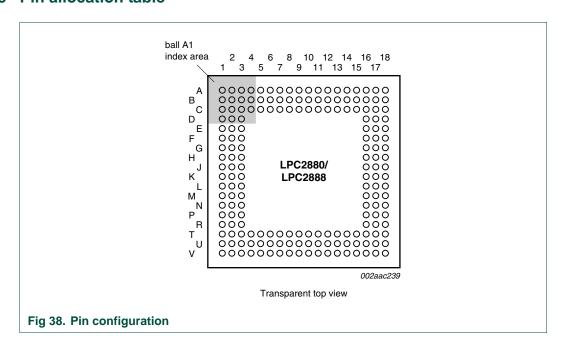

180 pin TFBGA package

# 3. Applications

- · Portable, battery powered devices

- USB devices

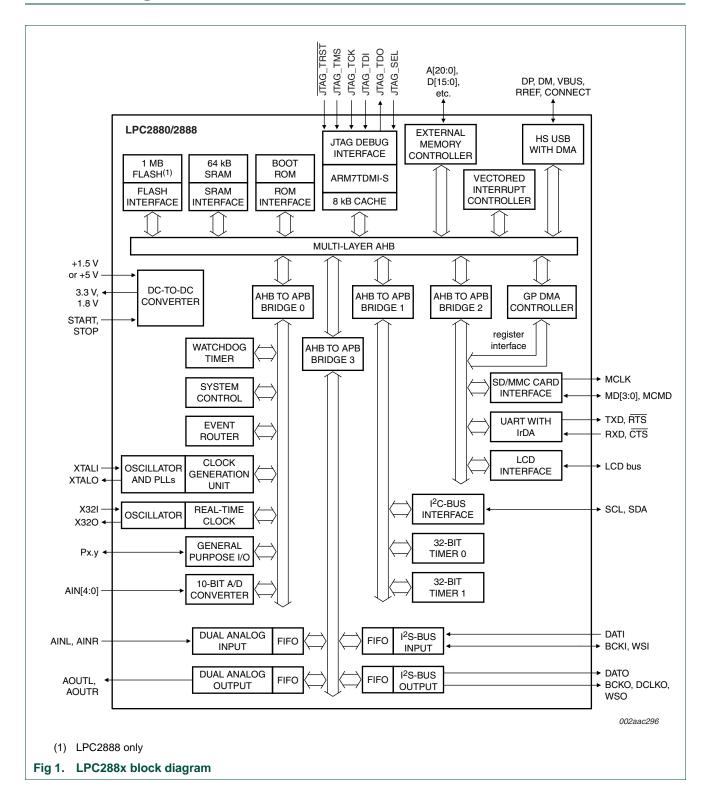

#### 4. Architectural overview

The LPC288x includes an ARM7TDMI CPU with an 8kB cache, an AMBA Advanced High-performance Bus (AHB) interfacing to high speed on-chip peripherals and internal and external memory, and four AMBA Advanced Peripheral Buses (APBs) for connection to other on-chip peripheral functions. The LPC288x permanently configures the ARM7TDMI processor for little-endian byte order.

The LPC288x includes a multi-layer AHB and four separate APBs, in order to minimize interference between the USB controller, other DMA operations, and processor activity. Bus masters include the ARM7 itself, the USB block, and the general purpose DMA controller.

Lower speed peripheral functions are connected to the APBs. Four AHB-to-APB bridges interface the APBs to the AHB.

# 5. ARM7TDMI processor

The ARM7TDMI is a general purpose 32 bit microprocessor that offers high performance and very low power consumption. The ARM architecture is based on Reduced Instruction Set Computer (RISC) principles, and the instruction set and related decode mechanism are much simpler than those of microprogrammed Complex Instruction Set Computers. This simplicity results in a high instruction throughput and impressive real-time interrupt response from a small and cost-effective processor core.

Pipeline techniques are employed so that all parts of the processing and memory systems can operate continuously. Typically, while one instruction is being executed, its successor is being decoded, and a third instruction is being fetched from memory.

The ARM7TDMI processor also employs a unique architectural strategy known as THUMB, which makes it ideally suited to high-volume applications with memory restrictions, or applications where code density is an issue.

The key idea behind THUMB is that of a super-reduced instruction set. Essentially, the ARM7TDMI processor has two instruction sets:

- The standard 32 bit ARM instruction set.

- A 16 bit THUMB instruction set.

The THUMB set's 16 bit instruction length allows it to approach twice the density of standard ARM code while retaining most of the ARM's performance advantage over a traditional 16 bit processor using 16 bit registers. This is possible because THUMB code operates on the same 32 bit register set as ARM code.

#### **Chapter 1: LPC2800 Introductory information**

THUMB code be as little as 65% of the code size of ARM, and 160% of the performance of an equivalent ARM processor connected to a 16 bit memory system.

The ARM7TDMI processor is described in detail on the ARM website.

## 6. On-Chip flash memory system

The LPC2888 includes a 1 MB Flash memory system. This memory may be used for both code and data storage. Programming of the Flash memory may be accomplished in several ways. It may be programmed In System via the USB port. The application program may also erase and/or program the Flash while the application is running, allowing a great degree of flexibility for data storage and field firmware upgrades.

The Flash is 128 bits wide and includes buffering to allow 3 out of 4 sequential read operations to operate without wait states.

# 7. On-Chip Static RAM

The LPC288x includes 64 kB of static RAM that may be used for code and/or data storage.

# 8. On-Chip ROM

The LPC288x includes 32 kB of Read Only Memory that may be used for code and/or constant storage. Execution begins in on-chip ROM after a Reset.

Philips provides a standard boot code in this ROM that reads the state of the Mode inputs and accordingly does one of the following:

- 1. starts execution in internal Flash,

- 2. starts execution in external memory,

- 3. performs a hardware self-test, or

- 4. downloads code from the USB interface into on-chip RAM and transfers control to the downloaded code.

#### **Chapter 1: LPC2800 Introductory information**

# 9. Block diagram

# **UM10208**

# Chapter 2: LPC2800 Memory addressing

Rev. 02 — 31 May 2007

**User manual**

# 1. Memory map and peripheral addressing

ARM processors have a single 4 GB address space. The following table shows how this space is used on the LPC288x. Addresses not shown in this table are not used.

Table 1. LPC288x memory usage

| Address range                 | General use     | Address range details and desc                          | ription                                                                                                   |

|-------------------------------|-----------------|---------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| 0x0000 0000 to                | Cacheable area  | 0x0020 0000 - 0x0020 7FFF                               | Internal ROM (32 kB)                                                                                      |

| 0x0FFF FFFF                   |                 | 0x0040 0000 - 0x0040 FFFF                               | Internal RAM (64 kB)                                                                                      |

|                               |                 | (other addresses)                                       | Software can map other internal and external memory into this area, to improve its effective access time. |

| 0x1000 0000 to<br>0x1FFF FFFF | Internal Memory | 0x1040 0000 - 0x104F FFFF                               | Flash (1 MB)                                                                                              |

| 0x2000 0000 to<br>0x5FFF FFFF | External Memory | 0x2000 0000 - 0x201F FFFF and 0x4000 0000 - 0x401F FFFF | Static memory bank 0, 2 MB, STCS0                                                                         |

|                               |                 | 0x2400 0000 - 0x241F FFFF and 0x4400 0000 - 0x441F FFFF | Static memory bank 1, 2 MB, STCS1                                                                         |

|                               |                 | 0x2800 0000 - 0x281F FFFF and 0x4800 0000 - 0x481F FFFF | Static memory bank 2, 2 MB, STCS2                                                                         |

|                               |                 | 0x3000 0000 - 0x33FF FFFF and 0x5000 0000 - 0x53FF FFFF | Dynamic memory bank 0, 64 MB                                                                              |

| 0x8000 0000 to<br>0x8FFF FFFF | Peripherals     | See <u>Table 2–2</u>                                    | Includes AHB Peripherals and 4 APBs                                                                       |

## 1.1 Memory map

The LPC2880/2888 memory map incorporates several distinct regions, as shown in <u>Figure 2–2</u>. When an application is running, the CPU interrupt vectors are remapped to allow them to reside in on-chip SRAM.

## Chapter 2: LPC2800 Memory mapping

|                   | reserved                     | 0x9000 0000 to 0xFFFF FFFF | 0xFFFF FFFF                |

|-------------------|------------------------------|----------------------------|----------------------------|

| peripherals {     | includes AHB and 4 APB buses | 0x8000 0000 to 0x8FFF FFFF | 0x9000 0000<br>0x8FFF FFFF |

| 2.0 GB }          |                              |                            | 0x8000 0000                |

|                   | reserved                     | 0x5400 0000 to 0x7FFF FFFF | 0x7FFF FFFF                |

|                   | dynamic memory bank 0, 64 MB | 0x5000 0000 to 0x53FF FFFF |                            |

|                   | reserved                     | 0x4820 0000 to 0x4FFF FFFF |                            |

| external memory   | static memory bank 2, 2 MB   | 0x4800 0000 to 0x481F FFFF |                            |

| (second instance) | reserved                     | 0x4420 0000 to 0x47FF FFFF |                            |

|                   | static memory bank 1, 2 MB   | 0x4400 0000 to 0x441F FFFF | -                          |

|                   | reserved                     | 0x4020 0000 to 0x43FF FFFF |                            |

|                   | static memory bank 0, 2 MB   | 0x4000 0000 to 0x401F FFFF | 0x4000 0000                |

| 1.0 GB            | reserved                     | 0x3400 0000 to 0x3FFF FFFF | 0x3FFF FFFF                |

|                   | dynamic memory bank 0, 64 MB | 0x3000 0000 to 0x33FF FFFF |                            |

|                   | reserved                     | 0x2820 0000 to 0x2FFF FFFF |                            |

| external memory   | static memory bank 2, 2 MB   | 0x2800 0000 to 0x281F FFFF |                            |

| (first instance)  | reserved                     | 0x2420 0000 to 0x27FF FFFF | <br>                       |

|                   | static memory bank 1, 2 MB   | 0x2400 0000 to 0x241F FFFF |                            |

|                   | reserved                     | 0x2020 0000 to 0x23FF FFFF | -]                         |

|                   | static memory bank 0, 2 MB   | 0x2000 0000 to 0x201F FFFF | 00000 0000                 |

|                   | reserved                     | 0x1050 0000 to 0x1FFF FFFF | 0x2000 0000<br>0x1FFF FFFF |

| internal memory < | internal flash (1 MB)        | 0x1040 0000 to 0x104F FFFF |                            |

|                   | reserved                     | 0x1000 0000 to 0x0000 003F | 0x1000 0000                |

|                   | reserved                     | 0x0050 0000 to 0x0FFF FFFF | 0x0FFF FFFF                |

|                   | internal RAM (64 kB)         | 0x0040 0000 to 0x0040 FFFF |                            |

| remapped area     |                              |                            |                            |

|                   | internal ROM (32 kB)         | 0x0020 0000 to 0x0020 7FFF |                            |

| 0.0 GB            | exception vectors            | 0x0000 0000 to 0x0000 001F | 0x0000 0000                |

|                   |                              |                            | 002aac240                  |

#### Chapter 2: LPC2800 Memory mapping

# 2. Peripheral addressing

Peripheral devices on the LPC288x are distributed among the ARM High-speed Bus (AHB) and four ARM Peripheral Buses (APBs). The following table indicates which bus each device is connected to. Addresses not shown in this table are not used.

Table 2. LPC288x Peripheral devices

| Address allocation        | Bus  | Register addresses (inclusive)                                                      | Peripheral device                                   |

|---------------------------|------|-------------------------------------------------------------------------------------|-----------------------------------------------------|

| 0x8000 0000 - 0x8000 1FFF | APB0 | 0x8000 0000 - 0x8000 1C00                                                           | Event Router                                        |

| 0x8000 2000 - 0x8000 23FF | APB0 | 0x8000 2000 - 0x8002 027C                                                           | Real Time Clock (RTC)                               |

| 0x8000 2400 - 0x8000 27FF | APB0 | 0x8000 2400 - 0x8000 2430                                                           | 10 bit Analog to Digital Converter (ADC)            |

| 0x8000 2800 - 0x8000 2BFF | APB0 | 0x8000 2800 - 0x8000 283C                                                           | Watchdog Timer (WDT)                                |

| 0x8000 3000 - 0x8000 3FFF | APB0 | 0x8000 3000 - 0x8000 31E8                                                           | I/O Configuration (IOCONF)                          |

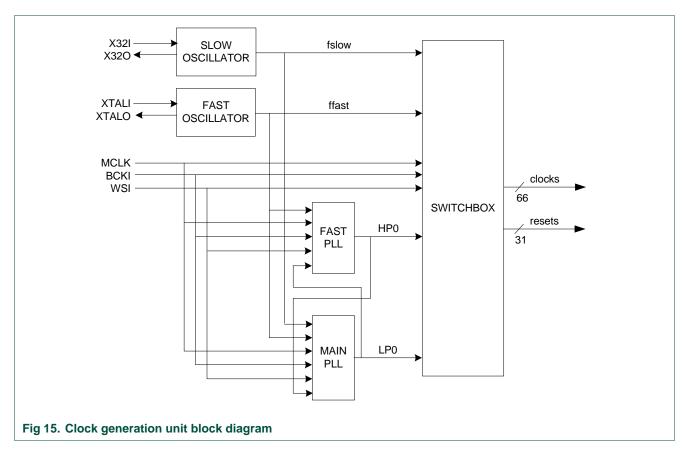

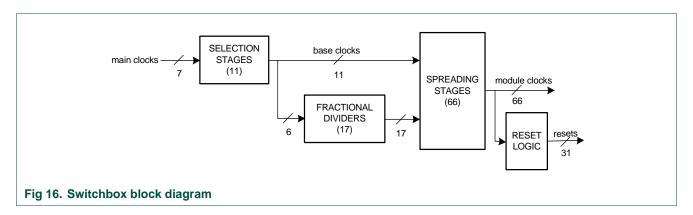

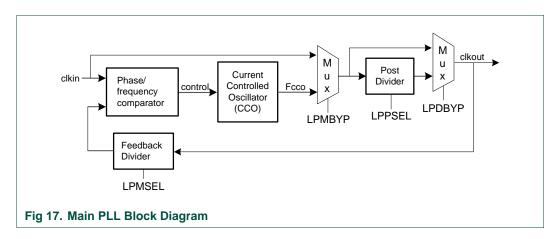

| 0x8000 4000 - 0x8000 4BFF | APB0 | 0x8000 4000 - 0x8000 443C                                                           | Clock Generation Unit (CGU) Switchbox               |

| 0x8000 4C00 - 0x8000 4FFF | APB0 | 0x8000 4C00 - 0x8000 4CFC                                                           | Clock Generation Unit (CGU)                         |

| 0x8000 5000 - 0x8000 53FF | APB0 | 0x8000 5000 - 0x8000 507C                                                           | System Configuration Registers                      |

| 0x8000 8000 - 0x8000 8FFF | AHB  | 0x8000 8000 - 0x8000 8258                                                           | External Memory Controller (EMC)                    |

| 0x8002 0000 - 0x8000 03FF | APB1 | 0x8002 0000 - 0x8002 0010                                                           | Timer 0                                             |

| 0x8002 0400 - 0x8000 07FF | APB1 | 0x8002 0400 - 0x8002 0410                                                           | Timer 1                                             |

| 0x8002 0800 - 0x8002 0BFF | APB1 | 0x8002 0800 - 0x8002 082C                                                           | I <sup>2</sup> C Controller                         |

| 0x8004 0000 - 0x8004 1FFF | AHB  | 0x8004 0000 - 0x8004 10B4                                                           | USB Controller                                      |

| 0x8010 0000 - 0x8010 0FFF | APB2 | 0x8010 0000 - 0x8010 00BC                                                           | Secure Digital / Multimedia Card Interface (SD/MCI) |

| 0x8010 1000 - 0x8010 1FFF | APB2 | 0x8010 1000 - 0x8010 1034<br>0x8010 1FD4 - 0x8010 1FEC                              | UART                                                |

| 0x8010 2000 - 0x8010 2FFF | APB2 | 0x8010 2000 - 0x8010 201C<br>0x8010 2FD8 - 0x8010 2FEC                              | Flash Programming Interface                         |

| 0x8010 3000 - 0x8010 33FF | APB2 | 0x8010 3000 - 0x8010 3080                                                           | LCD Interface                                       |

| 0x8010 3800 - 0x8010 3FFF | APB2 | 0x8010 3800 - 0x8010 38FC<br>0x8010 3A00 - 0x8010 3A7C<br>0x8010 3C00 - 0x8010 3C10 | GPDMA Controllers                                   |

| 0x8010 4000 - 0x8010 40FF | APB2 | 0x8010 4000 - 0x8010 4058                                                           | ARM7 cache control                                  |

| 0x8020 0000 - 0x8020 007F | APB3 | 0x8020 0000 - 0x8020 0078                                                           | Streaming Analog Input 1 (SAI1)                     |

| 0x8020 0180 - 0x8020 01FF | APB3 | 0x8020 0180 - 0x8020 01F8                                                           | Streaming Analog Input 4 (SAI4)                     |

| 0x8020 0200 - 0x8020 027F | APB3 | 0x8020 0200 - 0x8020 027C                                                           | Streaming Analog Output 1 (SAO1)                    |

| 0x8020 0280 - 0x8020 028F | APB3 | 0x8020 0280 - 0x8020 02FC                                                           | Streaming Analog Output 2 (SAO2)                    |

| 0x8020 0380 - 0x8020 03FF | APB3 | 0x8020 0380 - 0x8020 03BC                                                           | I <sup>2</sup> S and Streaming Analog Converters    |

| 0x8030 0000 - 0x8030 0FFF | AHB  | 0x8030 0000 - 0x8030 0474                                                           | Interrupt Controller                                |

# **UM10208**

# **Chapter 3: Boot process**

Rev. 02 — 31 May 2007

**User manual**

#### 1. Introduction

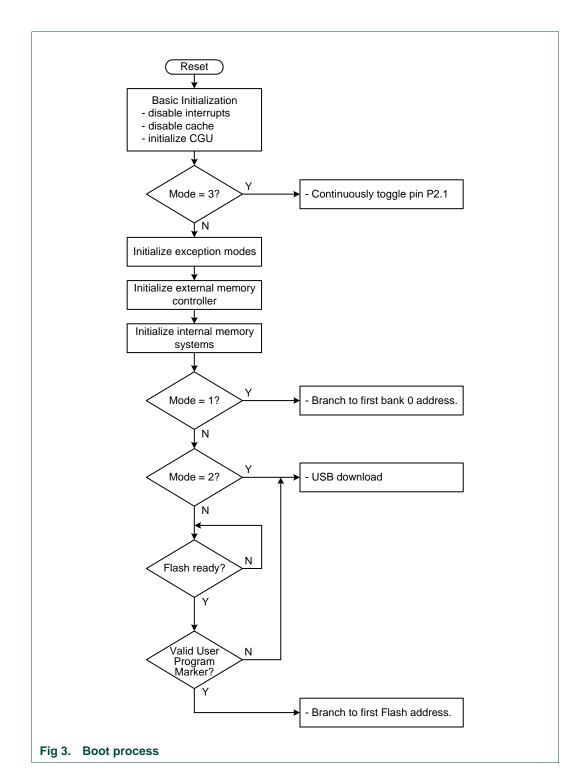

Upon reset, the LPC288x executes code from an internal ROM. This code allows four possible types of startup. These are:

- Execute code from internal flash memory.

- Execute code from external memory bank 0.

- Download code from USB to memory.

- Test mode. Toggles a port pin to indicate basic device functionality.

# 2. Operation

Internal pulldowns on the P2.3 and P2.2 pins cause them to read as 0 when unconnected. This results in the default startup mode being execution from internal Flash memory. One or two external pullup resistors can cause startup to use one of the other modes, as shown in Table 3–3.

Table 3. Boot flow chart

| P2.3/Mode2 | P2.2/Mode1 | Mode selected                                        |

|------------|------------|------------------------------------------------------|

| 0          | 0          | Execute user program from internal flash memory.     |

| 0          | 1          | Execute user program from external memory on bank 0. |

| 1          | 0          | Download program from USB port to memory.            |

| 1          | 1          | Test mode.                                           |

# 3. Boot mode descriptions

The boot process is illustrated in figure 1. The following discussion describes each boot mode in more detail.

#### Mode 0: Execute user program from internal flash memory

This is the default mode if the P2.3 and P2.2 pins are left unconnected. The Flash memory begins at address 0x1040\_0000. This is the address branched to in this mode.

In order to prevent accidental execution of an unprogrammed Flash, the ROM code checks for a specific valid user program marker value in memory prior to branching into the Flash memory. This marker is stored as address 0x104F\_F800, 2K bytes below the top of the 1MB Flash memory. The value expected here is 0xAA55\_AA55. If Mode 0 is selected and the valid user program marker value is not found in the Flash, control is transferred to Mode 2 (USB download mode).

Chapter 3: LPC2800 Boot process

#### Mode 1: Execute user program from external memory on static memory bank 0

Static bank 0 of external memory controller is used in a default configuration to execute a user program. The configuration of static bank 0 following reset is for a bus width of 16 bits and an active low chip select. The starting address used for the external static memory is 0x2000\_0000. The full address range for bank 0 is 0x4000\_0000 through 0x401F\_FFFF, a 2 megabyte space.

#### Mode 2: Download program from USB port to memory (DFU mode)

The purpose of this mode is to allow programming of the internal Flash memory via USB. Files to be download must be specially formatted in order to be handled by the ROM download code. A conversion program and a DFU downloader are available from Philips.

#### Mode 3: Test mode

This mode is a simple test for device function. Port pin P2.1 is toggled to indicate basic functionality of the device in its current environment.

**UM10208 NXP Semiconductors**

#### Chapter 3: LPC2800 Boot process

# Part Identification register (SYS\_PARTID - 0x8000 507C)

The SYS\_PARTID register contains a value that identifies this device.

#### **Chapter 3: LPC2800 Boot process**

Table 4: Part Identification register (SYS\_PARTID - 0x8000 507C)

| Bit  | Symbol  | Description                                | Reset<br>value |

|------|---------|--------------------------------------------|----------------|

| 31:0 | PART_ID | This value distinguishes this device type. | 0x0102 100A    |

# **UM10208**

# **Chapter 4: Processor cache and memory mapping**

Rev. 02 — 31 May 2007

**User manual**

#### 1. Introduction

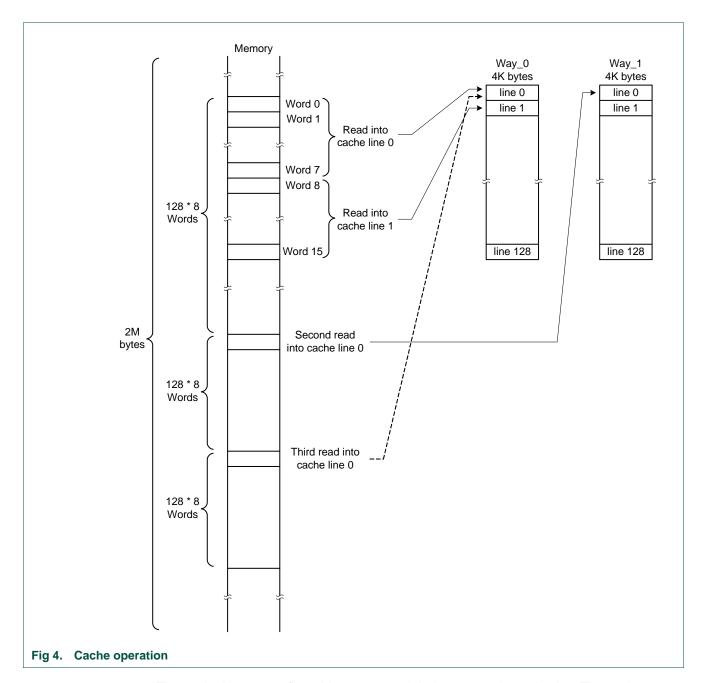

The ARM CPU in the LPC288x has been extended with a 2-way set-associative cache controller. The cache is 8 kB in size and can store both data and instruction code.

The biggest benefit of this cache is that if code is run from non-zero-wait state memory, for instance the internal FLASH controller, these memories can still behave almost as if they are zero-wait state memory. If code is executed from the cache, the CPU will run at 1 clock per instruction most of the time.

The trade-off in introducing this cache is that each AHB access that bypasses the cache will have an extra wait state inserted. So, it is generally advisable that both instruction caching and data caching are turned on for most regions of on and off-chip memory.

#### 2. Features

- 8 kB in a 2-way set-associative cache

- Configured as 2×128 cache lines of eight 32-bit words each

- Sixteen pages of address mapping each allow any address range to be selected for caching

#### 3. Cache definitions

- A 2-way cache includes two cache lines that can be used for each memory address.

- A cache line is 8 consecutive 32 bit words. The cache contains 128 cache lines, each with 2 ways, making 8 kB total.

- The association of memory addresses to cache lines is that cache line 0 corresponds with address word addresses 0x0 to 0x07, cache line 1 corresponds with word addresses 0x08 to 0x0F, etc. After 1024 words, this repeats. Thus, word address 0, word address 1024, word address 2048, ... all map to cache line 0.

- A tag word is associated with each cache line. The tag includes the address each

cache line is currently associated with, a "dirty" flag that indicates if the line has been

written to since it was read from memory, and a "Least Recently Used" tag that

identifies which of the two cache lines should be overwritten if another address that

maps there is accessed by the CPU.

- For the purposes of cache operation, memory is divided into pages of 2 megabytes, composed of 4 kB sub-pages (1024 words of 32 bits).

- A cache line is marked as "dirty" when the CPU writes to an address which is currently in the cache. In this case, the data in the "real" memory no longer reflects the actual value. The entire cache line is marked as dirty when any element within that cache line is written.

- A cache miss is defined as a read or write by the CPU to an address in memory which is not currently in the cache.

Chapter 4: LPC2800 Cache

- A cache hit is defined as a read or write by the CPU to an address in memory which is currently in cache.

- A cache flush is the act of writing a dirty cache line back to memory.

# 4. Description

<u>Figure 4–4</u> shows the structure of the cache and how memory addresses map to cache lines. For caching purposes, memory is divided into pages of 2 megabytes of 4 kB sub-pages (1024 words of 32 bits). The sub-pages correspond to 128 cache lines (128 entries of eight 32-bit words).

The associated cache line in memory will be stored in cache memory at a fixed position. An example sequence could begin with an access to one of the first 8 words of a 2 megabyte page of memory. These words will be stored on the first cache line (cache line 0) of Way\_0. An access to one of the second 8 words in the same page will be stored on the second cache line (cache line 1) of Way\_0. Later, if an address that maps to cache line 0 is read from a different portion of memory, it will be stored in Way\_1 (since Way\_1 has not yet been used). If still another address mapping to cache line 0 is read, the Least Recently Used tag is used to decide whether the new line will be stored in Way\_0 or Way\_1. The least recently used previously cached line must be removed, and the new line stored in its place. In this example, the way that is overwritten will be Way\_0, since Way\_1 was used more recently. If the cache line that must be removed is marked as "dirty", it will be written back to memory prior to being overwritten by the new memory line.

Note that the cache can be set to work only for instruction accesses, only for data accesses, or for both. This is done via the DATA\_ENABLE and INSTRUCTION\_ENABLE bits in the CACHE\_SETTINGS register.

Chapter 4: LPC2800 Cache

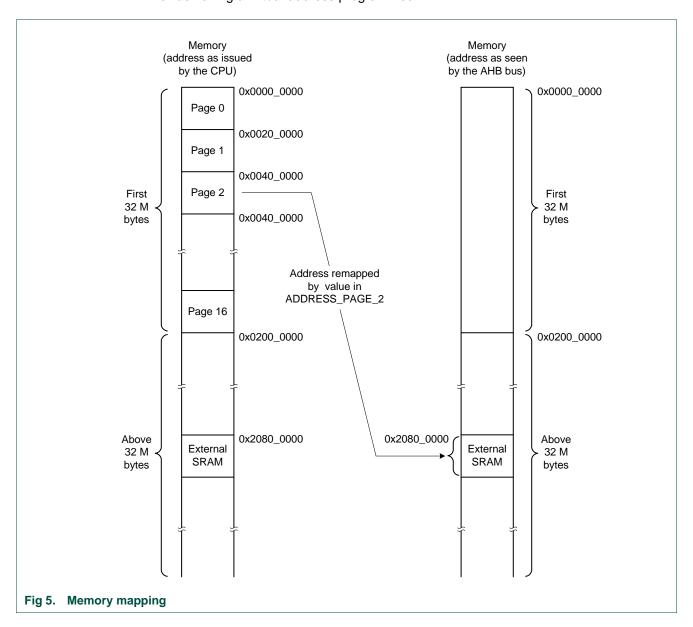

The cache has 16 configurable pages, each being 2 megabytes in size. The cache treats these 16 pages as if they occupy the bottom 32 Megabytes of the system memory map, which is their default mapping. The cache can re-map any of these pages such that the physical address is above the lower 32 megabytes.

In <u>Figure 4–5</u>, a diagram showing physical memory and a virtual page mapping is given. On the left of the diagram, memory is shown with no remapping, as issued by the CPU. On the right, a higher physical address is shown mapped into a lower address for caching purposes. To accomplish this, a page is used as a virtual page. Accessing this virtual page, the cache will re-map the AHB bus address to the higher address range during a cache miss, cache flush or a write access to the virtual page.

Chapter 4: LPC2800 Cache

In <u>Figure 4–5</u>, page 2 of the lower 32 megabytes of address space has been mapped to an address in the external static memory space by placing a value of 0x104 in the PAGE\_ADDRESS\_2 register. Details of this remapping may be found in the descriptions of the PAGE\_ADDRESS registers later in this chapter.

When re-mapping points to a higher page in the memory map, that page may still also be accessed directly by the CPU using the original absolute address of the page. In that case, the cache takes no part in the access. This allows both cached and non-cached access to the same address region if needed.

Each of the 16 configurable cache pages can be individually enabled and disabled, as well as having a virtual address programmed.

Chapter 4: LPC2800 Cache

#### 4.1 Cache enabling and function

Following reset, the cache is disabled. The address, data, and control signals of the CPU AHB bus is routed directly to the multilayer AHB matrix. The response from whichever functional block is targeted by the address is routed directly to the CPU.

The cache can be enabled by setting the DATA\_ENABLE and/or INSTRUCTION\_ENABLE bits in the CACHE\_SETTINGS register.

#### 4.1.1 Cache function details

For each page of the cache which is enabled, the following points apply:

- If data is read, and not in the cache (a cache miss), a line of eight 32-bit words is read

from the AHB bus. In the meantime, the CPU is stalled (and in low power mode if

clock gating is enabled.)

- If data is read and is found in the cache (a cache hit), data is read from cache with 0

wait states

- If data is written and the location is not in the cache (a cache miss), the data is written directly to memory.

- If data is written, and the location is in the cache because this location has been read before (a cache hit), then data is written to the cache with 0 wait states, and the line is marked as dirty.

- If a dirty line is about to be discarded because of a cache miss (the cache line needs

to be reused for a different memory region), the old line is first written back to memory

(a cache line flush).

- When a cache line is read from memory and stored in the cache (in Way\_0 or Way\_1), the cache controller will mark the other half of the cache line at the same address as Least Recently Used (LRU) in its tag memory.

# 5. Register description

The cache controller includes the registers shown in <u>Table 4–5</u>. These registers are accessible in the APB2 address space. It is recommended that the clock gating option be enabled in the CGU for the APB interface of the CPU in order to reduce power consumption. Each register is described in more detail in the following sections.

Note: the APB interface of the CPU configuration hardware must be set to run at the same BASE\_CLK frequency as the AHB interface of the CPU before any register is written.

Table 5. Cache and memory mapping registers

| Address     | Register name   | Description                                                                                                                                                                     | Reset<br>value | Access |

|-------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------|--------|

| 0x8010 4000 | CACHE_RST_STAT  | Monitors the reset state of the cache.                                                                                                                                          | 0              | RO     |

| 0x8010 4004 | CACHE_SETTINGS  | Controls the overall configuration of the cache.                                                                                                                                | 0              | R/W    |

| 0x8010 4008 | CACHE_PAGE_CTRL | Allows individual enabling or disabling of caching for the 16 configurable pages.                                                                                               | 0              | R/W    |

| 0x8010 400C | C_RD_MISSES     | If cache performance analysis is enabled in the CACHE_SETTINGS register, this register indicates the number of times that a cache line is read from memory (cache read misses). | 0              | RO     |

UM10208 2 © NXP B.V. 2007. All rights reserved

Chapter 4: LPC2800 Cache

Table 5. Cache and memory mapping registers

| Address     | Register name   | Description                                                                                                                                                                                   | Reset value | Access |

|-------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--------|

| 0x8010 4010 | C_FLUSHES       | If cache performance analysis is enabled in the CACHE_SETTINGS register, this register indicates the number of times that a dirty cache line has been written back to memory (cache flushes). | 0           | RO     |

| 0x8010 4014 | C_WR_MISSES     | If cache performance analysis is enabled in the CACHE_SETTINGS register, this register indicates the number of times that a write occurs to an address not in the cache (cache write misses). | 0           | RO     |

| 0x8010 4018 | PAGE_ADDRESS_0  | Re-mapping address for page 0.                                                                                                                                                                | 0           | R/W    |

| 0x8010 401C | PAGE_ADDRESS_1  | Re-mapping address for page 1. The reset value points this page to the Boot ROM.                                                                                                              | 0x1         | R/W    |

| 0x8010 4020 | PAGE_ADDRESS_2  | Re-mapping address for page 2. The reset value points this page to the on-chip SRAM.                                                                                                          | 0x2         | R/W    |

| 0x8010 4024 | PAGE_ADDRESS_3  | Re-mapping address for page 3. The reset value points this page to the on-chip SRAM.                                                                                                          | 0x2         | R/W    |

| 0x8010 4028 | PAGE_ADDRESS_4  | Re-mapping address for page 4. The reset value points this page to on-chip Flash memory.                                                                                                      | 0x82        | R/W    |

| 0x8010 402C | PAGE_ADDRESS_5  | Re-mapping address for page 5. The reset value points this page to external static memory bank 0.                                                                                             | 0x100       | R/W    |

| 0x8010 4030 | PAGE_ADDRESS_6  | Re-mapping address for page 6. The reset value points this page to external static memory bank 0.                                                                                             | 0x100       | R/W    |

| 0x8010 4034 | PAGE_ADDRESS_7  | Re-mapping address for page 7. The reset value points this page to external SDRAM.                                                                                                            | 0x180       | R/W    |

| 0x8010 4038 | PAGE_ADDRESS_8  | Re-mapping address for page 8. The reset value points this page to external SDRAM.                                                                                                            | 0x180       | R/W    |

| 0x8010 403C | PAGE_ADDRESS_9  | Re-mapping address for page 9.                                                                                                                                                                | 0x400       | R/W    |

| 0x8010 4040 | PAGE_ADDRESS_10 | Re-mapping address for page 10.                                                                                                                                                               | 0x401       | R/W    |

| 0x8010 4044 | PAGE_ADDRESS_11 | Re-mapping address for page 11.                                                                                                                                                               | 0x102       | R/W    |

| 0x8010 4048 | PAGE_ADDRESS_12 | Re-mapping address for page 12.                                                                                                                                                               | 0x104       | R/W    |

| 0x8010 404C | PAGE_ADDRESS_13 | Re-mapping address for page 13.                                                                                                                                                               | 0x106       | R/W    |

| 0x8010 4050 | PAGE_ADDRESS_14 | Re-mapping address for page 14.                                                                                                                                                               | 0xE         | R/W    |

| 0x8010 4054 | PAGE_ADDRESS_15 | Re-mapping address for page 15.                                                                                                                                                               | 0xF         | R/W    |

| 0x8010 4058 | CPU_CLK_GATE    | Controls gating of the CPU clock when the CPU is stalled.                                                                                                                                     | 0           | R/W    |

## 5.1 Cache Reset Status register (CACHE\_RST\_STAT, 0x8010 4000)

The read-only CACHE\_RST\_STAT register monitors the reset status of the cache controller. If the CACHE\_RST bit in the CACHE\_SETTINGS register is set and then cleared by software, this bit indicates the status of the ongoing reset. The reset of the cache tag memory will take 128 CPU clock-cycles to complete. <u>Table 4–6</u> shows the bit definitions for the CACHE\_RST\_STAT register.

Chapter 4: LPC2800 Cache

Table 6. Cache Reset Status register (CACHE\_RST\_STAT, 0x8010 4000)

| Bit  | Symbol       | Description                                                                                                                                                        | Reset value |

|------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 0    | CACHE_STATUS | <ul><li>0: Cache reset is complete.</li><li>1: Cache reset is ongoing.</li><li>When the cache is reset, software should poll CACHE_STATUS until it is 0.</li></ul> | 0           |

| 31:1 | -            | Reserved. The value read from a reserved bit is not defined.                                                                                                       | -           |

# 5.2 Cache Settings register (CACHE\_SETTINGS, 0x8010 4004)

The CACHE\_SETTINGS register controls the general setup of the cache, allows resetting of the entire cache, and controls the cache performance analysis feature. <u>Table 4–7</u> shows the bit definitions for the CACHE\_SETTINGS register.

Table 7. Cache Settings register (CACHE\_SETTINGS, 0x8010 4004)

| Bit | Symbol             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Reset value |

|-----|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 0   | CACHE_RST          | Cache controller reset control. This bit resets the cache hardware internally, clearing all tags so that the entire cache is considered empty. This takes 128 CPU clock cycles to complete. The reset progress can be followed by reading register CACHE_RST_STAT.  0: De-assert reset to the Flash controller.  1: Assert reset to the Flash controller.  Note: the cache MUST be reset before it is enabled. It is recommended to include this procedure at system startup. | 0           |

| 1   | DATA_ENABLE        | Enables use of the cache for storing data.                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0           |

|     |                    | 0 : All storage of data in the cache is disabled. This applies to all 16 pages.                                                                                                                                                                                                                                                                                                                                                                                               |             |

|     |                    | 1 : Storage of data in the cache is enabled. This applies to all pages enabled via the CACHE_PAGE_CTRL register.                                                                                                                                                                                                                                                                                                                                                              |             |

| 2   | INSTRUCTION_ENABLE | Enables use of the cache for storing instructions.                                                                                                                                                                                                                                                                                                                                                                                                                            | 0           |

|     |                    | 0 : All storage of instructions in the cache is disabled. This applies to all 16 pages.                                                                                                                                                                                                                                                                                                                                                                                       |             |

|     |                    | 1 : Storage of instructions in the cache is enabled. This applies to all pages enabled via the CACHE_PAGE_CTRL register.                                                                                                                                                                                                                                                                                                                                                      |             |

Chapter 4: LPC2800 Cache

Table 7. Cache Settings register (CACHE\_SETTINGS, 0x8010 4004)

| Bit  | Symbol        | Description                                                                                                                                                                                                                      | Reset value |

|------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 3    | PERF_ANAL_RST | Allows a software reset of the cache performance analysis counters in the registers C_RD_MISSES, C_FLUSHES, and C_WR_MISSES.                                                                                                     | 0           |

|      |               | 0 : Allow performance analysis counters to run, if enabled.                                                                                                                                                                      |             |

|      |               | 1 : Reset the cache performance analysis counters. This has an effect only if performance analysis is enabled.                                                                                                                   |             |

| 4    | PERF_ANAL_ENA | Controls the cache performance analysis counters in the registers C_RD_MISSES, C_FLUSHES, and C_WR_MISSES. Performance analysis should be disabled when not needed in order to save power.  0: Performance analysis is disabled. | 0           |

|      |               | Performance analysis is enabled.                                                                                                                                                                                                 |             |

| 31:5 | -             | Reserved. Do not write 1s to reserved bits. The values                                                                                                                                                                           | -           |

|      |               | read from reserved bits is not defined.                                                                                                                                                                                          |             |

# 5.3 Cache Page Enable Control register (CACHE\_PAGE\_CTRL, 0x8010 4008)

The CACHE\_PAGE\_CTRL register allows individual enabling of caching of each of the 16 pages. <u>Table 4–8</u> shows the bit definitions for the CACHE\_PAGE\_CTRL register.

Table 8. Cache Page Enable Control register (CACHE\_PAGE\_CTRL, 0x8010 4008)

| Bit | Symbol      | Description                                                   | Reset<br>value |

|-----|-------------|---------------------------------------------------------------|----------------|

| 0   | PAGE_0_ENA  | This bit enables caching for page 0.                          | 0              |

|     |             | 0: Caching for this page is disabled.                         |                |

|     |             | 1: Caching for this page is enabled.                          |                |

| 1   | PAGE_1_ENA  | This bit enables caching for page 1, as described for bit 0.  | 0              |

| 2   | PAGE_2_ENA  | This bit enables caching for page 2, as described for bit 0.  | 0              |

| 3   | PAGE_3_ENA  | This bit enables caching for page 3, as described for bit 0.  | 0              |

| 4   | PAGE_4_ENA  | This bit enables caching for page 4, as described for bit 0.  | 0              |

| 5   | PAGE_5_ENA  | This bit enables caching for page 5, as described for bit 0.  | 0              |

| 6   | PAGE_6_ENA  | This bit enables caching for page 6, as described for bit 0.  | 0              |

| 7   | PAGE_7_ENA  | This bit enables caching for page 7, as described for bit 0.  | 0              |

| 8   | PAGE_8_ENA  | This bit enables caching for page 8, as described for bit 0.  | 0              |

| 9   | PAGE_9_ENA  | This bit enables caching for page 9, as described for bit 0.  | 0              |

| 10  | PAGE_10_ENA | This bit enables caching for page 10, as described for bit 0. | 0              |

| 11  | PAGE_11_ENA | This bit enables caching for page 11, as described for bit 0. | 0              |

| 12  | PAGE_12_ENA | This bit enables caching for page 12, as described for bit 0. | 0              |

| 13  | PAGE_13_ENA | This bit enables caching for page 13, as described for bit 0. | 0              |

Chapter 4: LPC2800 Cache

| Table 8. Cache | Page Enable | Control register | (CACHE | PAGE | CTRL. | . 0x8010 4008) |

|----------------|-------------|------------------|--------|------|-------|----------------|

|----------------|-------------|------------------|--------|------|-------|----------------|

| Bit   | Symbol      | Description                                                                                    | Reset value |

|-------|-------------|------------------------------------------------------------------------------------------------|-------------|

| 14    | PAGE_14_ENA | This bit enables caching for page 14, as described for bit 0.                                  | 0           |

| 15    | PAGE_15_ENA | This bit enables caching for page 15, as described for bit 0.                                  | 0           |

| 31:16 | -           | Reserved. Do not write 1s to reserved bits. The values read from reserved bits is not defined. | -           |

Note: If data caching has been enabled for a writable page, and software then disables caching, there may be "dirty data" in the cache that still needs to be written to memory.

#### 5.4 Cache Read Misses counter (C\_RD\_MISSES, 0x8010 400C)

The C\_RD\_MISSES register allows reading the number of times that a cache line fill has occurred (a cache read miss) since the last time that the performance analysis registers have been reset. The counter only operates if performance analysis has been enabled via the PERF\_ANAL\_ENA bit in the CACHE\_SETTINGS register. In order to save power, performance analysis should be turned off if it is not actually being used.

## 5.5 Cache Flushes counter (C\_FLUSHES, 0x8010 4010)

The C\_FLUSHES register allows reading the number of times that a cache line has been written back to memory (a cache flush) since the last time that the performance analysis registers have been reset. A cache line is written back to memory only if it has been marked as dirty (due to its contents being changed) and the cache line is subsequently required for normal continuing cache operation. The counter only operates if performance analysis has been enabled via the PERF\_ANAL\_ENA bit in the CACHE\_SETTINGS register. In order to save power, performance analysis should be turned off if it is not actually being used.

#### 5.6 Cache Write Misses counter (C\_WR\_MISSES, 0x8010 4014)

The C\_WR\_MISSES register allows reading the number of times that a write has occurred to a memory address that is not in the cache (a cache write miss). The counter only operates if performance analysis has been enabled via the PERF\_ANAL\_ENA bit in the CACHE\_SETTINGS register. In order to save power, performance analysis should be turned off if it is not actually being used.

# 5.7 Page Address Pointer Registers (PAGE\_ADDRESS0:15, 0x8010 4018:4054)

The 16 PAGE\_ADDRESS registers allow remapping of addresses in the range supported by the cache (the bottom 32 megabytes of memory space) so that they apply to other address ranges. When the CPU performs an access to an address in the cache range, any value in the related PAGE\_ADDRESS register will replace the top 11 bits of the 32-bit address. By leaving the bottom 21 bits unaltered, each increment of the value in an PAGE\_ADDRESS register corresponds to a shift of 2 megabytes. In this manner, software can control which memory address ranges are cached.

For example, if the CPU accesses the address 0x0121\_4A90, and the PAGE\_ADDRESS\_9 register contains the value 0x82, caching activity and the CPU access will apply to address 0x1041\_4A90:

#### Chapter 4: LPC2800 Cache

| Original address:0121_4A90 =                        | <u>0000 0001 001</u> 0 0001 _ 0100 1010 1001 0000 |

|-----------------------------------------------------|---------------------------------------------------|

| Top 11 address bits removed:                        | <u>0000 0000 000</u> 0 0001 _ 0100 1010 1001 0000 |

| Address bits from PAGE_ADDRESS9 (082) =             | 0001 0000 010                                     |

| <pre>Top 11 address bits replaced:1041_4A90 =</pre> | <u>0001 0000 010</u> 0 0001 _ 0100 1010 1001 0000 |

This particular setting maps page 9 of the cacheable address space to the on-chip Flash memory starting at address 0x1040\_0000.

<u>Table 4–9</u> shows the address ranges covered by each of the PAGE\_ADDRESS registers, and <u>Table 4–10</u> shows the use of bits in each register.

Table 9. Address ranges used by PAGE\_ADDRESS registers

| Register        | 2 megabyte<br>multiple | Bottom of related address range | Top of related address range |

|-----------------|------------------------|---------------------------------|------------------------------|

| PAGE_ADDRESS_0  | 0                      | 0x0000 0000                     | 0x001F FFFF                  |

| PAGE_ADDRESS_1  | 1                      | 0x0020 0000                     | 0x003F FFFF                  |

| PAGE_ADDRESS_2  | 2                      | 0x0040 0000                     | 0x005F FFFF                  |

| PAGE_ADDRESS_3  | 3                      | 0x0060 0000                     | 0x007F FFFF                  |

| PAGE_ADDRESS_4  | 4                      | 0x0080 0000                     | 0x009F FFFF                  |

| PAGE_ADDRESS_5  | 5                      | 0x00A0 0000                     | 0x00BF FFFF                  |

| PAGE_ADDRESS_6  | 6                      | 0x00C0 0000                     | 0x00DF FFFF                  |

| PAGE_ADDRESS_7  | 7                      | 0x00E0 0000                     | 0x00FF FFFF                  |

| PAGE_ADDRESS_8  | 8                      | 0x0100 0000                     | 0x011F FFFF                  |

| PAGE_ADDRESS_9  | 9                      | 0x0120 0000                     | 0x013F FFFF                  |

| PAGE_ADDRESS_10 | 10                     | 0x0140 0000                     | 0x015F FFFF                  |

| PAGE_ADDRESS_11 | 11                     | 0x0160 0000                     | 0x017F FFFF                  |

| PAGE_ADDRESS_12 | 12                     | 0x0180 0000                     | 0x019F FFFF                  |

| PAGE_ADDRESS_13 | 13                     | 0x01A0 0000                     | 0x01BF FFFF                  |

| PAGE_ADDRESS_14 | 14                     | 0x01C0 0000                     | 0x01DF FFFF                  |

| PAGE_ADDRESS_15 | 15                     | 0x01E0 0000                     | 0x01FF FFFF                  |

Table 10. Page Address Pointer Registers (PAGE\_ADDRESS0:15, 0x8010 4018:4054)

| Bit   | Symbol    | Description                                                                                                                                                                                                                   | Reset<br>value   |

|-------|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 10:0  | UPPR_ADDR | This value will replace the top 11 bits of the 32-bit address coming from the CPU. When the CPU performs an access to the related page, the address which is placed on the AHB bus will depend on the value of this register. | see<br>Table 4–5 |

| 31:11 | -         | Reserved. Do not write 1s to reserved bits. The values read from reserved bits is not defined.                                                                                                                                | -                |

#### 5.8 CPU Clock Gate control (CPU\_CLK\_GATE, 0x8010 4058)

The CPU\_CLK\_GATE register allows saving power by gating the CPU clock when the CPU is stalled waiting for bus access. <u>Table 4–11</u> shows the bit definitions for the CPU\_CLK\_GATE register.

Chapter 4: LPC2800 Cache

Table 11. CPU Clock Gate control (CPU\_CLK\_GATE, 0x8010 4058)

| Bit  | Symbol       | Description                                                                                                                                                | Reset value |

|------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| 0    | CPU_CLK_GATE | This bit controls clock gating to the CPU. When clock gating is enabled, power is saved by not clocking the CPU when it is stalled waiting for bus access. | 0           |

|      |              | 0: The CPU clock is running continuously.                                                                                                                  |             |

|      |              | 1: The CPU clock is gated off while the CPU is stalled.                                                                                                    |             |

| 31:1 | -            | Reserved. Do not write 1s to reserved bits. The values read from reserved bits is not defined.                                                             | -           |

# 6. Cache programming procedures

#### 6.1 Cache initialization

1. Clear the cache:

Set and reset the CACHE\_RST bit in the CACHE\_SETTINGS register (one clock cycle is sufficient).

The status flag CACHE\_RST\_STAT in the CACHE\_STATUS indicates whether a cache reset is ongoing. Software should poll this bit before the cache is enabled.

2. Program the virtual address for each page, if needed:

Software can enable those parts of the memory map that are to be cacheable, by setting the appropriate bits in the CACHE\_PAGE\_CTRL register.

Each bit represents one page (2 megabytes) of memory space:

- bit 0 enables 0x0000\_0000 to 0x0020\_0000 as cached (page 0),

- bit 1 enables 0x0020\_0000 to 0x0040\_0000 as cached (page 1),

- bit 2 enables 0x0040\_0000 to 0x0060\_0000 as cached (page 2),

- etc.

- 3. Program the virtual address for each page, if needed:

The 11 bits programmed for each page represents the top 11 bits of a 32-bit address that will be put on the AHB bus. This allows any part of the entire 32-bit address range to be remapped into the bottom 32 megabytes of space, in pages of 2 megabytes. The PAGE\_ADDRESS registers DO NOT reset to a value such that remapping is not in force, so they should always be initialized even if remapping is not needed in the application.

#### Example:

Say address location 0x10400000 (in on-chip Flash) must be mapped for page 3. That can be done this way:

```

*PAGE_ADDRESS_3 = (0x10400000 >> 21); // = 0x082;

```

If the CPU reads address 0x00600004 (an address inside page 3) , then address 0x10400004 is provided to the AHB bus.

Note: care must be taken if remapping a page from which the code is currently running, or a page that is being used for data, stack or heap storage.

4. Enable the cache for data and /or instructions:

Enable the cache by setting the DATA\_ENABLE and/or INSTRUCTION\_ENABLE bits in the CACHE\_SETTINGS register.

Chapter 4: LPC2800 Cache

For enabling cache functions, these two bits apply to all cache pages that are enabled via the CACHE\_PAGE\_CTRL register. For disabling cache functions, these bits apply to all 16 cache pages, regardless of the setting of the CACHE\_PAGE\_CTRL register.

The entire cache can be programmed to:

- cache only instructions

- cache only data

- cache both instructions and data

If neither of the two enable bits is set, the cache is disabled.

#### 6.2 Cache flushing

Cache flushing may be required if caching of data is enabled, or when the virtual address of a page must be changed while this page has caching enabled. Cache flushing is only necessary if data-caching is enabled.

If data is written to cached memory, the new data will initially end up only inside the cache, and the related cache line marked as dirty. This data is not yet stored in the true physical location in memory. Since the cache applies only to the ARM7, not to other AHB masters, if another master (such as the GPDMA) is programmed to copy this data, it will copy the old data. If the programmer wants to guarantee that the data inside the cache is written to memory, the programmer has to flush the cache.

The cache controller does not include a direct method to cause an immediate cache flush. If software needs to flush the entire cache, a simple way to accomplish this is to fill the cache with read-only data (for instance ROM data). This results in every cache line being checked to see if it is dirty, and written back to memory if needed. Only 1 out of the 8 words from memory corresponding to each cache line must be read in order to flush one cache line. A total of 256 cache lines must be read in order to fully flush the cache. Below is a C language example to replace the cache contents, thereby flushing its the cache.

```

void flush_cache (int * cache_start) {

volatile int * flush_pointer = (volatile int *) cache_start;

volatile int cache_dummy;

int i;

for (i=0;i<2048;i+=8) cache_dummy = flush_pointer[i];

}</pre>

```

Example: Calling the flush\_cache procedure with a value of 0x1200 will read 8 kB of read-only code starting from 0x1200 into the cache, effectively flushing all dirty data from the cache.

A subset of this procedure could be used to flush a portion of the cache (as little as one cache line) if the line and its original address is known. Any two data locations other than the location of the currently cached data that maps to the same cache line can be read. This will cause any of the originally cached data to be flushed if it is marked as dirty.

Cache flushing may be necessary in the following cases:

Chapter 4: LPC2800 Cache

- 1. When data caching is enabled for a page, and another bus master such as the GPMA uses this data as well.

- When data caching is enabled for a page, and caching for this page is about to be disabled. When the caching for a page is disabled, every word is read directly from memory, bypassing the cache. If any data has been written to that page, the CPU may read the wrong data.

- 3. When data caching in the CACHE\_SETTINGS register is about to be disabled. This is a more general version of case 2.

- 4. When the virtual address of a cached page is about to be changed. This applies for both instruction and data caching. The cache controller is not aware of any changes made to the address mapping. If the address mapping is changed, software must ensure that any altered cache contents are flushed. Also, if code was executed from the page that is about to be remapped, it must be flushed to prevent later execution of the wrong instructions.

#### 6.3 Avoiding cache flushing

It may be possible to avoid cache flushing in some cases. If the performance difference is not critical, data caching can simply not be enabled. Performance reductions in the 20 to 30% range are possible if data caching is disabled, depending on the application.

Another way to avoid data caching in certain cases is to have 2 pages that point to the same memory address range. One page would be set as cacheable, the other as not cacheable. Data written to the non-cached page is written directly to memory, so other bus masters can make use of this data without any need to flush the cache. Care must be taken not to write data to one page, and read the same data from the other page. This can be done by separating portions of the page that may be changing from portions that will not be changing. Changeable portions would be both read and written in the non-cached address range, while static data would be read from the cached address range.

#### 6.4 CPU and cache clocking

The CPU clocking is somewhat different than the rest of the AHB system. Where the rest of the AHB system is clocked by the CGU (the AHB-BASE\_CLOCK, possibly modified by a fractional divider), the CPU and cache system use the AHB clock as a reference to generate internal clocks from the AHB\_BASE\_CLOCK. Inside the cache system is a clock-gate that uses the reference clock to enable or disable the base clock going to the CPU and cache system.

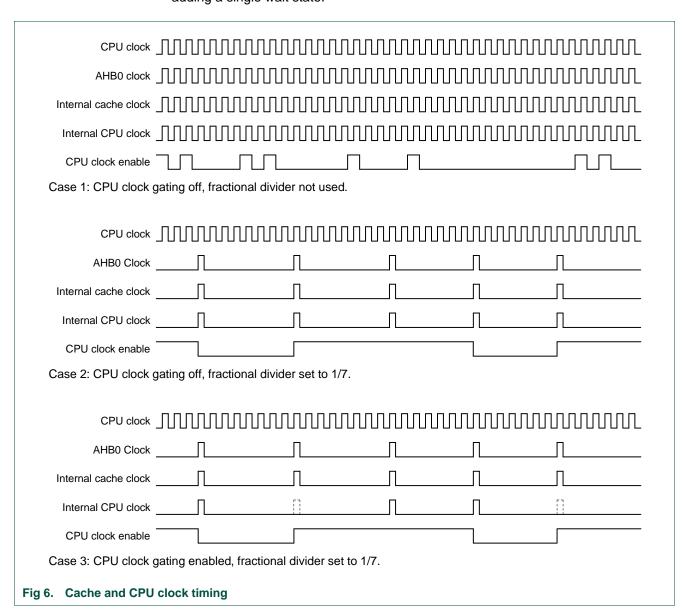

<u>Figure 4–6</u> shows timing of some cases of different clock selection settings. These figures show some internal signals to illustrate the timing. First, "CPU clock" is the clock as seen by the CPU. Second, "CPU clock enable" is the signal that determines when the CPU receives a clock when clock gating is enabled. The CPU clock enable signal goes low one AHB clock prior to the time when the CPU clock is prevented.

Following is a description of each case shown:

CPU clock gating off, fractional divider not used.

In this case, there is no CPU clock-gating and a fractional divider for the AHB clock is not selected. This results in a free-running clock for the AHB, cache and CPU, all running at the same frequency. This is the reset condition of the system.

Chapter 4: LPC2800 Cache

- CPU clock gating off, fractional divider set to 1/7.

In this case, the AHB fractional divider has been set to generate a bus clock once every 7 base clock cycles.

- 3. CPU clock gating enabled, fractional divider set to 1/7.

In this case, CPU clock gating has been enabled. The CPU clock enable signal is generated by the cache when the CPU must wait because either the cache is reading or writing data on the AHB bus, or the cache is jumping in between cache lines, adding a single wait state.

# **UM10208**

# **Chapter 5: Flash interface and programming**

Rev. 02 — 31 May 2007

**User manual**

#### 1. Introduction

The LPC2888 includes one megabyte of flash memory. This memory is located on the AHB and is accessible by all AHB masters. In contrast, the LPC2880 does not include any on-chip flash memory.

#### 2. Features

- Flash memory is an AHB slave for data transfer.

- APB slave interface for programmatic flash programming and erasure.

- Interrupt capability when flash erasure or programming is completed.

# 3. Description

The flash memory controller has an AHB slave port for transfer of instructions and data to the CPU in response to normal read requests. There is also a APB port for configuring the Flash controller and for accomplishing programming functions.

#### 3.1 Flash organization

The Flash memory is organized into 64 kB large sectors and 8 kB small sectors. For 1 MB of total Flash, there are 15 large sectors and 8 small sectors. The organization of these sectors and corresponding address ranges is shown in <u>Figure 5–7</u>.

The flash memory produces 128 bits of data for each read operation. These four words of data are referred to as a flash word. During programming, four flash words are programmed at a time.

#### 3.2 Flash buffering

Because the Flash memory is 128 bits wide, while the AHB is a 32 bit interface, a buffer between the Flash memory and the AHB can reduce power by limiting the number of Flash reads required, as well as speed up response to reads of consecutive Flash locations.

A Flash read is a slow process compared to the AHB cycle time. With buffering, the average read time is reduced, which can improve system performance. A single level buffer receives data from a Flash read and retains it until another flash read is required. When an AHB read requires data from the same Flash Word as the previous read, a Flash read is not performed, and read data is given without wait states. During sequential program execution, a Flash read will only be required for every fourth ARM instruction, or every eighth Thumb instruction.

When an AHB read requires data from a different Flash Word than the previous read, a new Flash read is performed and wait states occur until the new read data is available.

The flash buffer is automatically invalidated after:

Chapter 5: LPC2800 Flash

- Chip initialization

- An access to a flash configuration register

- Data latch reading (described in <u>Section 5–4 "In-Application flash programming" on page 30)</u>

| 8KB small sector # 7   | 0x104F_E000 to 0x104F_FFFF |

|------------------------|----------------------------|

| 8KB small sector # 6   | 0x104F_C000 to 0x104F_DFFF |

| 8KB small sector # 5   | 0x104F_A000 to 0x104F_BFFF |

| 8KB small sector # 4   | 0x104F_8000 to 0x104F_9FFF |

| 8KB small sector # 3   | 0x104F_6000 to 0x104F_7FFF |

| 8KB small sector # 2   | 0x104F_4000 to 0x104F_5FFF |

| 8KB small sector # 1   | 0x104F_2000 to 0x104F_3FFF |

| 8KB small sector # 0   | 0x104F_0000 to 0x104F_1FFF |

| 64KB large sector # 14 | 0x104E_0000 to 0x104E_FFFF |

| 64KB large sector # 13 | 0x104D_0000 to 0x104D_FFFF |

| 64KB large sector # 12 | 0x104C_0000 to 0x104C_FFFF |

| 64KB large sector # 11 | 0x104B_0000 to 0x104B_FFFF |

| 64KB large sector # 10 | 0x104A_0000 to 0x104A_FFFF |

| 64KB large sector # 9  | 0x1049_0000 to 0x1049_FFFF |

| 64KB large sector # 8  | 0x1048_0000 to 0x1048_FFFF |

| 64KB large sector # 7  | 0x1047_0000 to 0x1047_FFFF |

| 64KB large sector # 6  | 0x1046_0000 to 0x1046_FFFF |

| 64KB large sector # 5  | 0x1045_0000 to 0x1045_FFFF |

| 64KB large sector # 4  | 0x1044_0000 to 0x1044_FFFF |

| 64KB large sector # 3  | 0x1043_0000 to 0x1043_FFFF |

| 64KB large sector # 2  | 0x1042_0000 to 0x1042_FFFF |

| 64KB large sector # 1  | 0x1041_0000 to 0x1041_FFFF |

| 64KB large sector # 0  | 0x1040_0000 to 0x1040_FFFF |

|                        |                            |

Fig 7. Flash sector organization

Chapter 5: LPC2800 Flash

#### 3.3 Wait state programming

The Flash controller takes data from the memory after a predefined number of clock cycles. These clock cycles are called wait states and can be programmed in the WAIT\_STATES field of the F\_WAIT register. The optimal number of wait states depends on the clock frequency of the AHB clock. As a result, the number of wait states should typically be changed if the CPU clock rate is changed. To prevent incorrect reads, wait states should be changed to a larger value just **before** increasing the CPU clock rate, or changed to a smaller value just **after** decreasing the CPU clock rate.

# 4. In-Application flash programming

#### 4.1 Introduction

Programming the embedded flash memory requires a specific sequence of events, controlled primarily by software.

The flash memory is organized in sectors, as shown in <u>Figure 5–7</u>, that must be erased before data can be written into them. The flash memory also has built in protection against accidental programming.

As software write words to addresses in the Flash memory address range (0x104x xxxx), the hardware transfers a Flash word (4 words, 16 bytes) into an internal page buffer, after each write to an address 0x104x xxxC. A Flash page is the unit in which the Flash is programmed: 512 bytes.

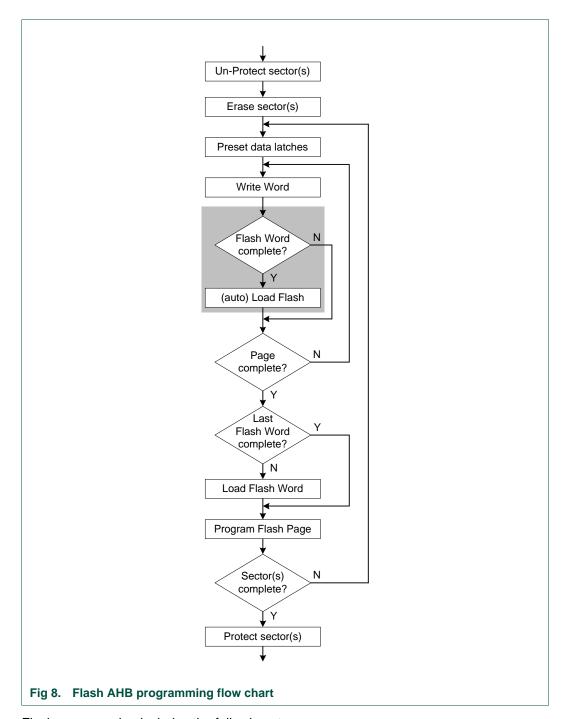

<u>Figure 5–8</u> shows a flow chart for programming the flash memory on the LPC2888. The shaded part of the flow chart represents functions that are done automatically by the hardware of the flash controller.

Chapter 5: LPC2800 Flash

Flash programming includes the following steps:

- 1. Un-protecting the sectors to be operated upon

- 2. Erasing sectors that have been previously programmed

- 3. Presetting data latches for each flash word to be programmed

- 4. Writing

- 5. Loading

- 6. Programming

Chapter 5: LPC2800 Flash